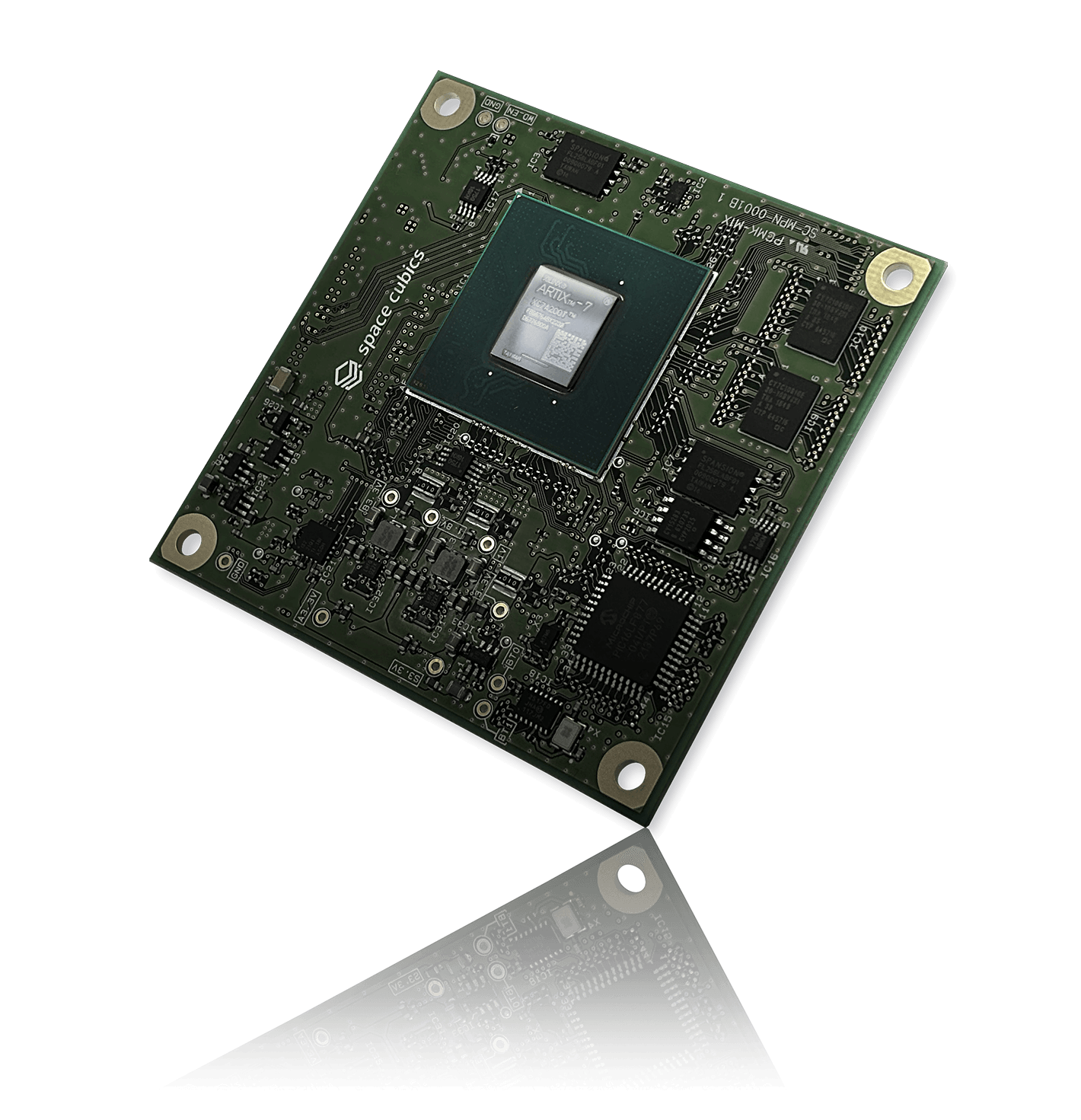

SC-OBC MODULE A1

TOP/product details/SC-OBC Module A1

Product overview

Use cases

Dev kit

Specifications

Docs / resources

PRODUCT

The SC-OBC MODULE A1 board is optimized for use in CubeSats. We use technology cultivated by JAXA for reliable, safe use on the International Space Station. These boards use a Xilinx Artix-7 FPGA, allowing flexible configuration and multiple interface options. Not limited to CubeSats, our boards can also benefit other spacecraft and even terrestrial applications here on Earth.

USES

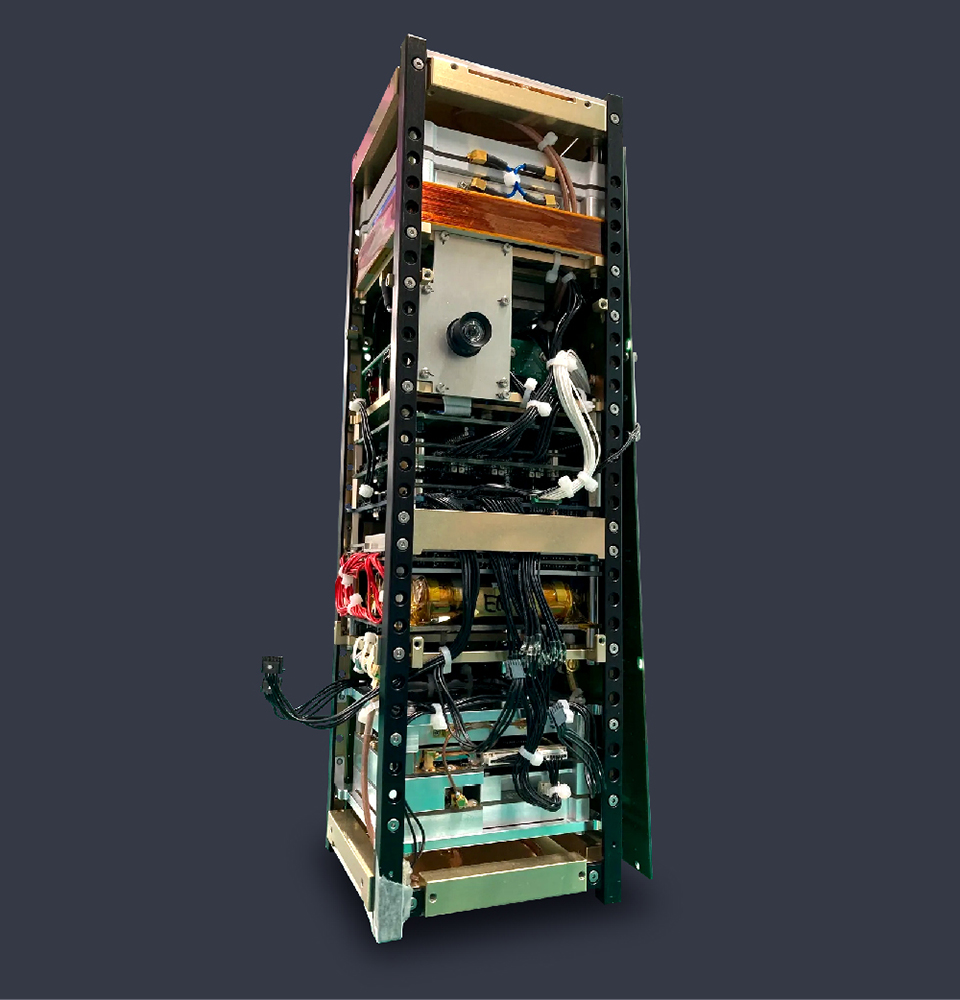

During installation in our own satellite,

the SC-OBC Module A1 board was mounted to an interface board with a PC104 form factor.

the SC-OBC Module A1 board was mounted to an interface board with a PC104 form factor.

A satellite equipped with the SC-OBC Module A1 installed on an interface board.

(Photo shows a prototype under development)

(Photo shows a prototype under development)

DEV KIT

development set

coming soon

optional items

coming soon

SPECS

Main Processor

Xilinx Artix-7

Main CPU

Cortex-M3 / MicroBlaze-V

Preinstalled OS

Zephyr RTOS

Clock Generator

24 MHz x 2

PIC (anomaly detection / system recovery)

8 bit PIC MCU

On-chip SRAM

64 KByte FPGA Block RAM

On-board SRAM

4 MBytes

NOR Flash Memory (configurable)

32 MBytes x 2

FeRAM

512 KBytes x 2

Communication Interface

CAN, I2C, UART

FPGA User I/O

38 pin

PIC User I/O

3 pin

Watchdog timer

1 (IP Core)

Interface Connector

80 pin / 0.5 mm pitch

Supply Voltage

DC 5.0 V ± 10%

Power Consumption

2.0 W (Max)

External Dimensions

70 x 70 x 9.6 mm

Mass

130 g

DOCS

This repository serves as documentation on SC-OBC Module A1 specifications, communication systems, circuit configurations, and more.